++++++++++++++++++++++++++++++++++++++++++++++++++++++

萩原良昭(76歳)個人活動の紹介です

( 2024年10月5日(土) 20:00 p.m. 現在 )

萩原 aips 研究所が創る人工知能(AI)搭載のロボット.pdf

搭載のロボット.jpg)

半導体未来館(マンガ館)のご紹介です

Publication_List_by_Yoshiaki_Hagiwara.html

++++++++++++++++++++++++++++++++++++++++++++++++++++++

TENA.html

************************************************************************************

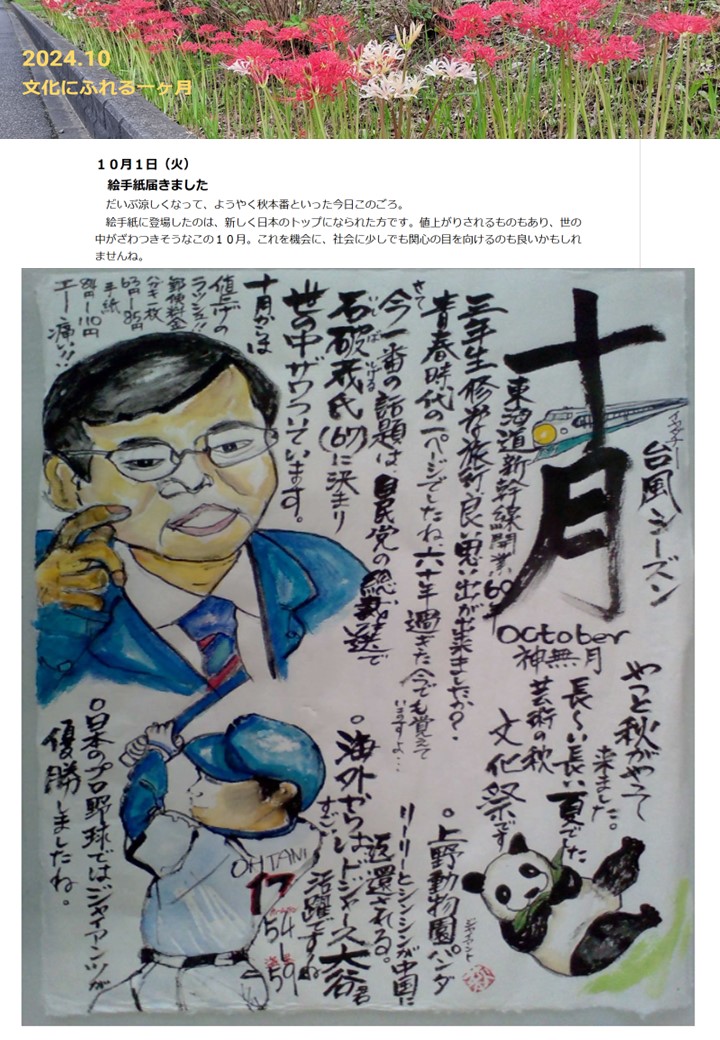

萩原トミエの絵手紙_Backup_2024年7月迄

萩原トミエの絵手紙雑記帳_令和4年5月から

++++++++++++++++++++++++++++++++++++++++++++++++++++++

厚木市荻野中学校/学校日記/2024-10

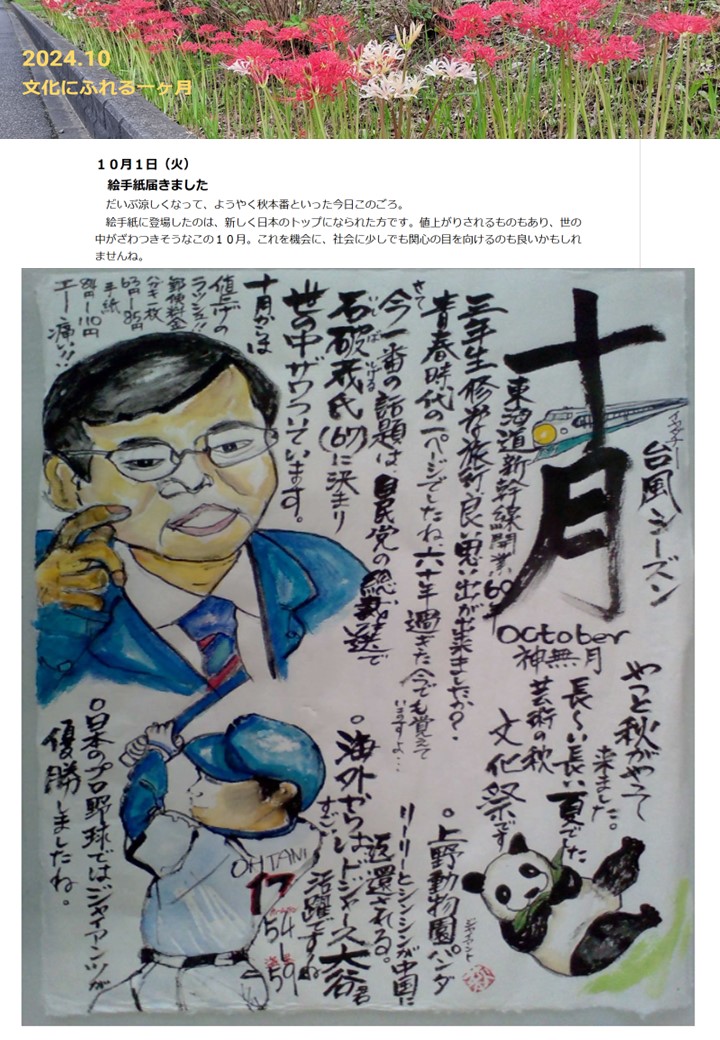

E_Tegami_of_Tomie_Hagiwara_2024_10.pdf

Tomie_Hagiwara_E_Tegam_Backups(2022.04~2024/10).html

++++++++++++++++++++++++++++++++++++++++++++++++++++++

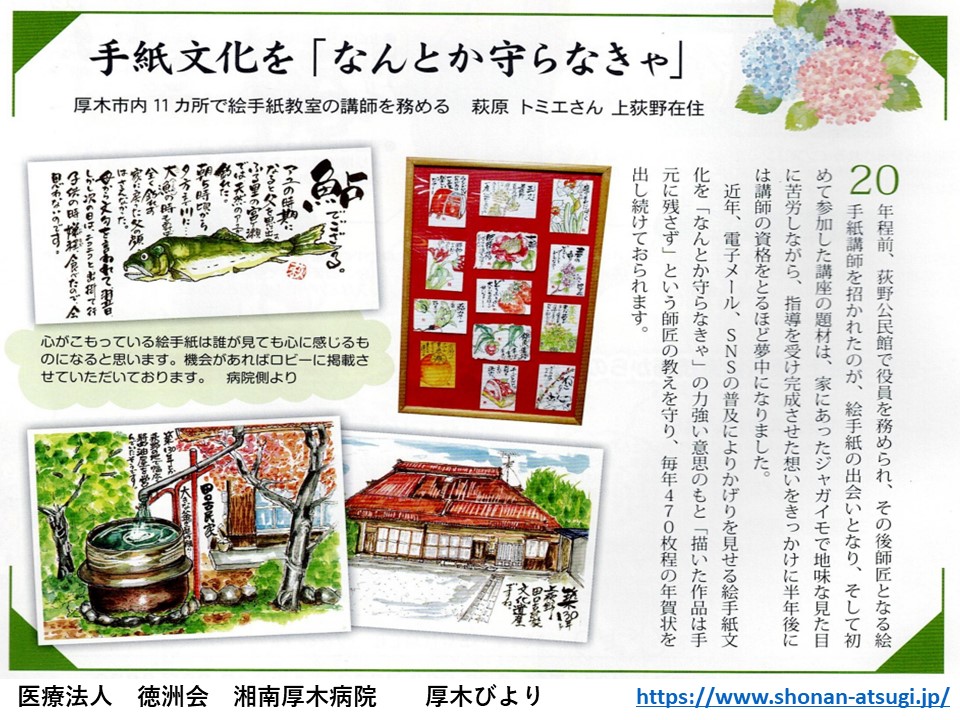

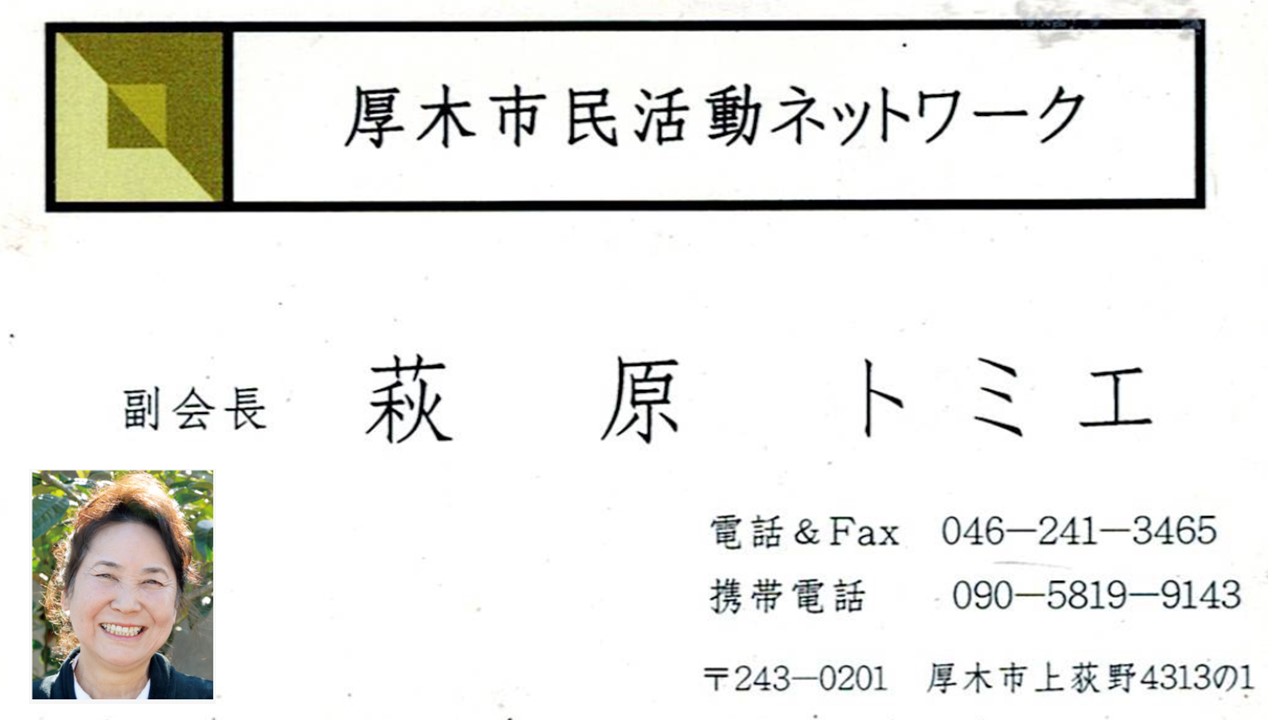

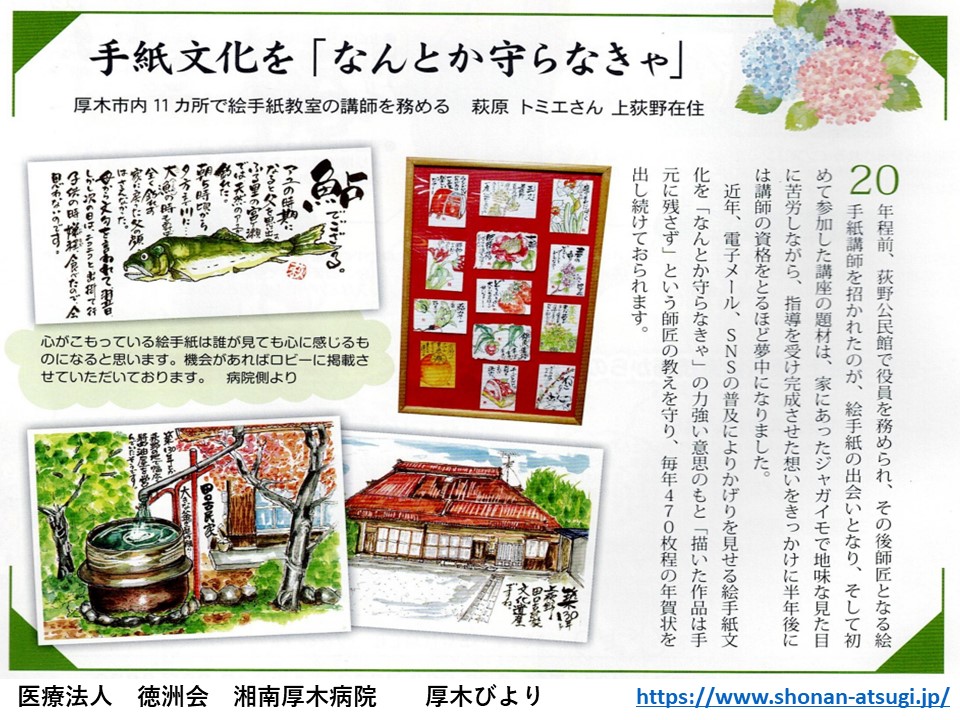

神奈川県全域「タウンニュース」_2019年1月18日掲載記事_萩原トミエ

++++++++++++++++++++++++++++++++++++++++++++++++++++++

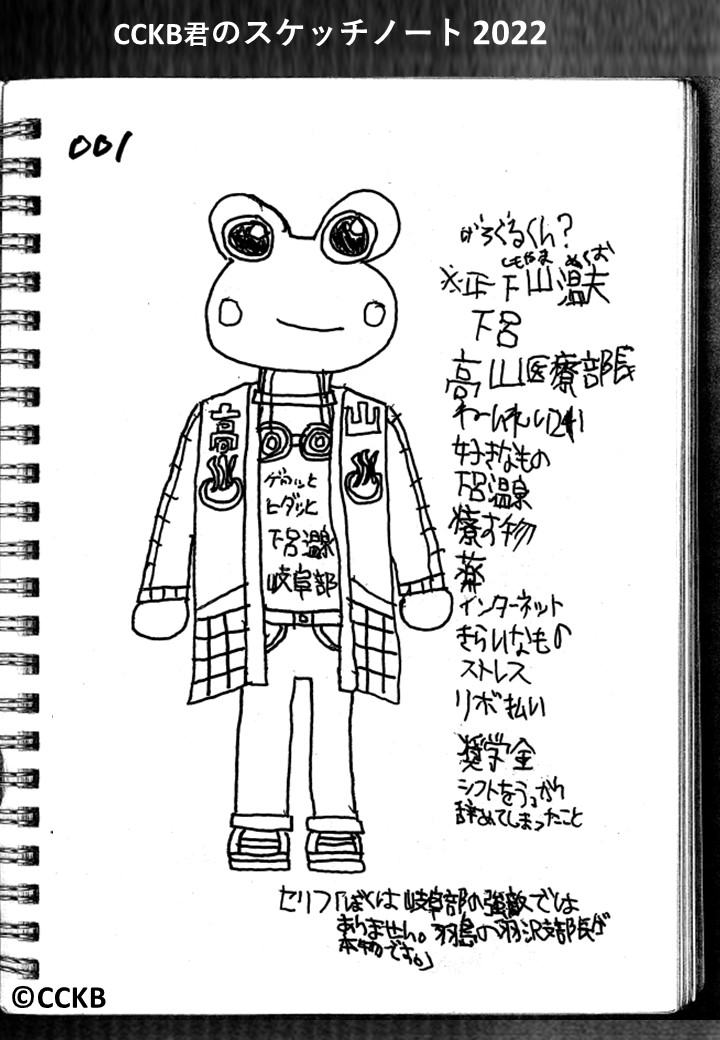

第05冊目_CCKB君のスケッチノート2022.html

第06冊目_CCKB君のスケッチノート2023_Sketch001~022.html

第07冊目_CCKB君のスケッチノート2023_Sketch023~049.html

第08冊目_CCKB君のスケッチノート_2023_03_16.html

第09冊目_CCKB君のスケッチノート_2023_04_02.html

第09A冊目_CCKB君のスケッチノート_2023_06_28.html

第10冊目_CCKB君のスケッチノート_2023_05_16.html

第11冊目_CCKB君のスケッチノート_2023_06_19.html

第12冊目_CCKB君のスケッチノート_2023_07_04.html

第13冊目_CCKB君のスケッチノート_2023_10_04.html

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

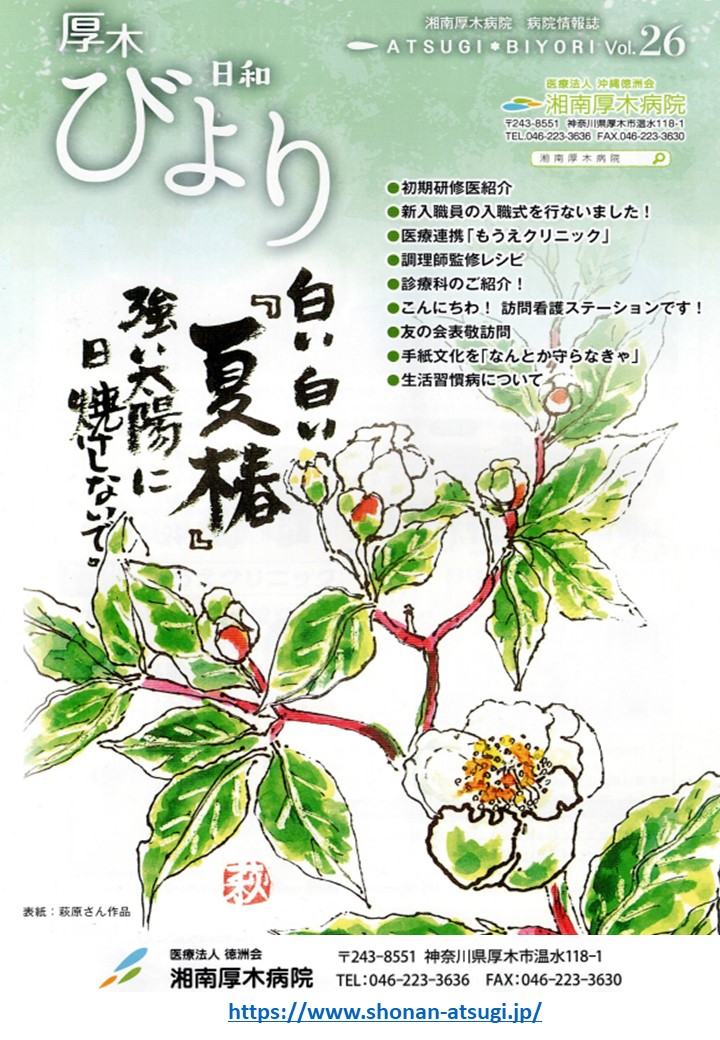

2019_Summer_厚木びより_Vol_26_Page_07_E_Tegami_by_Hagiwara_Tomie.pdf

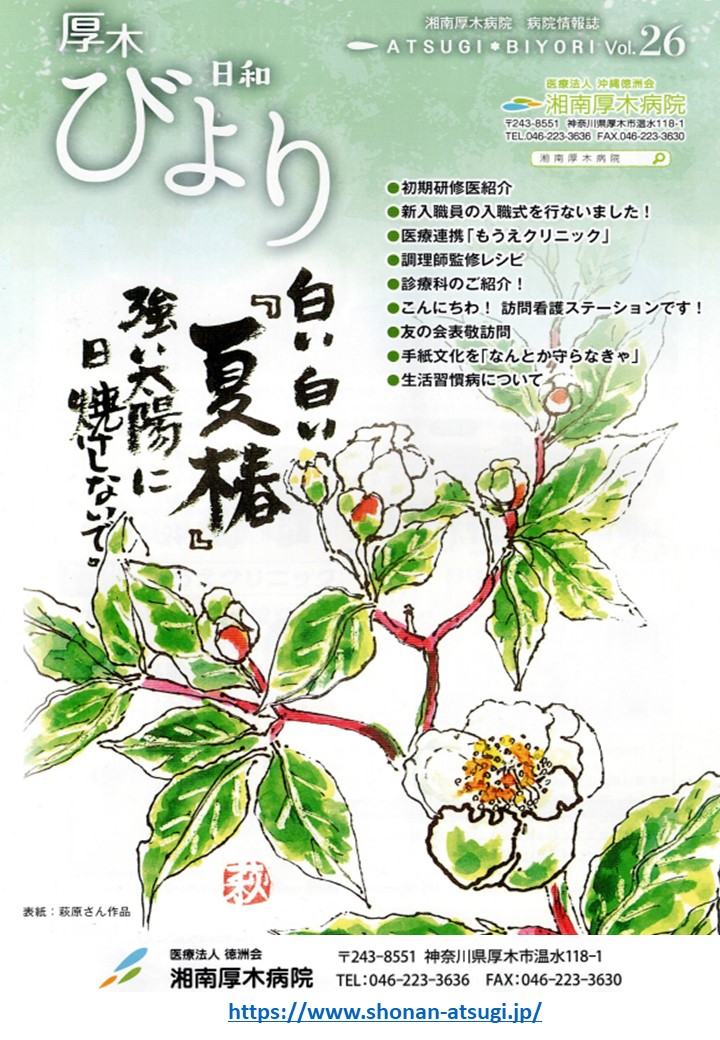

2019_Spring_厚木びより_Vol_26_表紙_E_Tegami_by_Hagiwara_Tomie.pdf

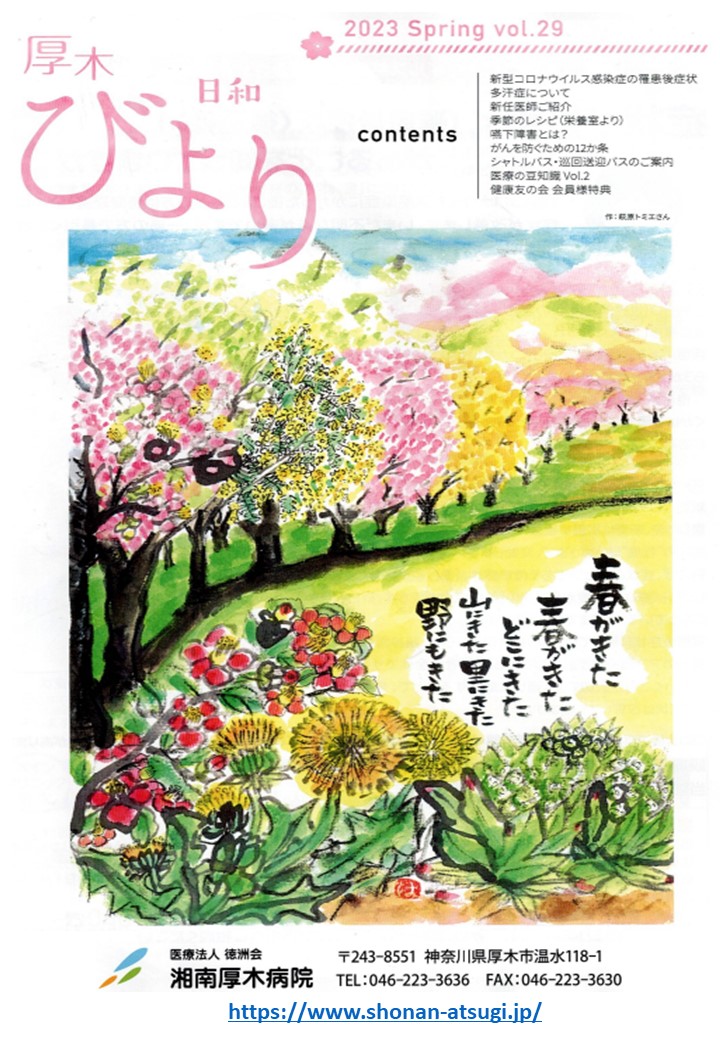

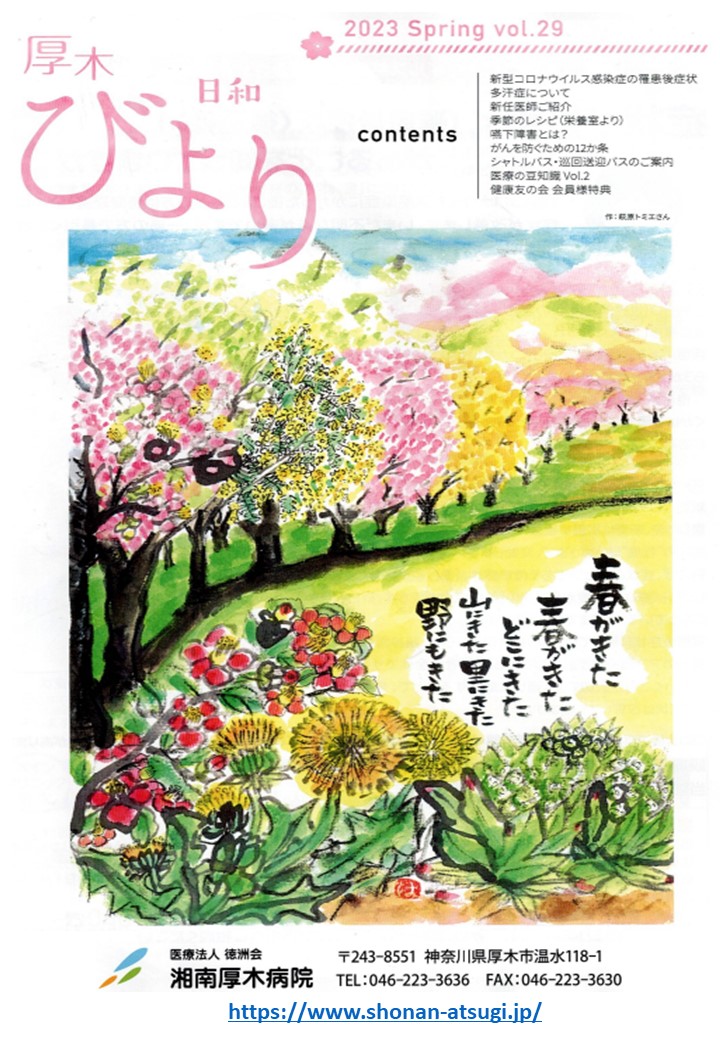

2023_Spring_厚木びより_Vol_29_表紙_E_Tegami_by_Hagiwara_Tomie.pdf

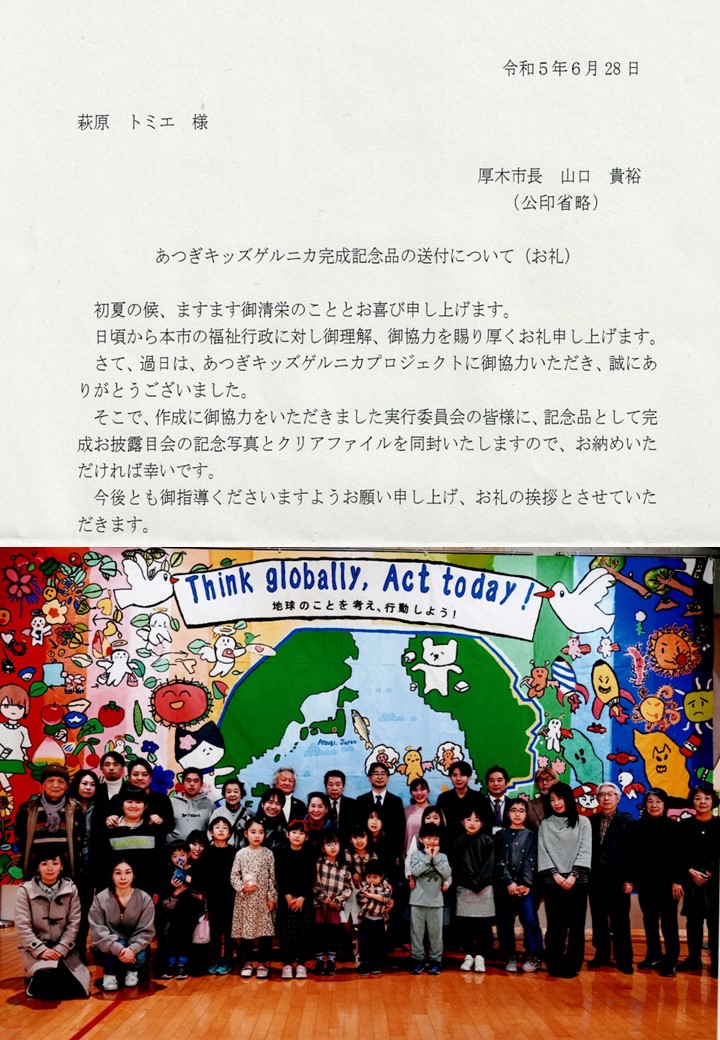

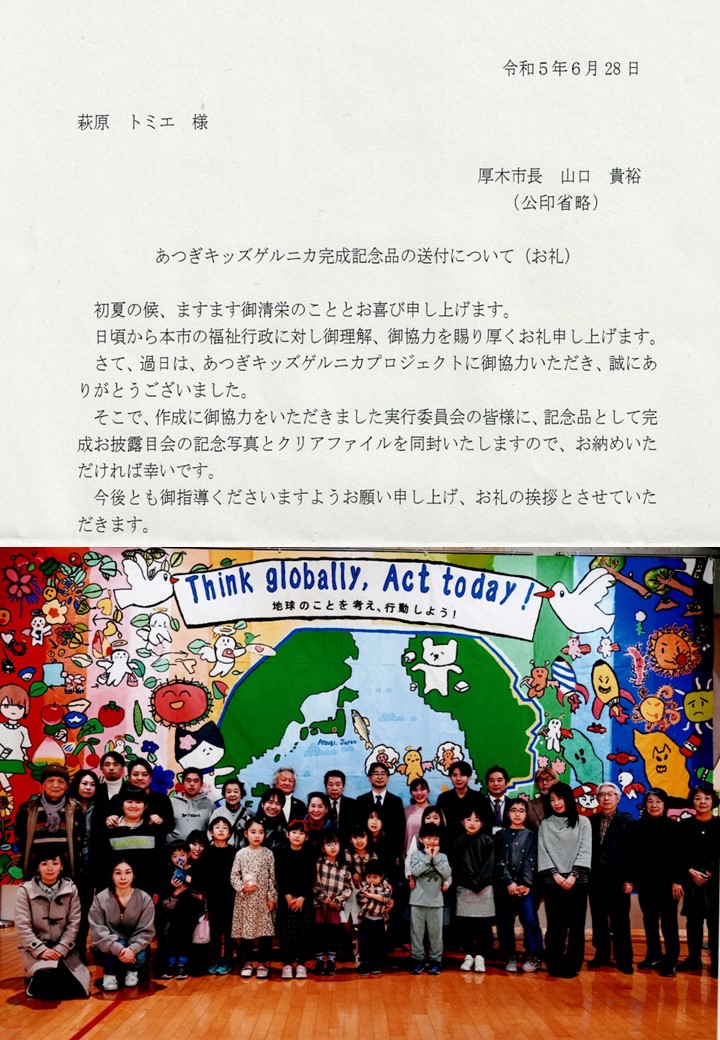

Atsugi-city_Kids_Gernica_Project_2023_1_29.pdf

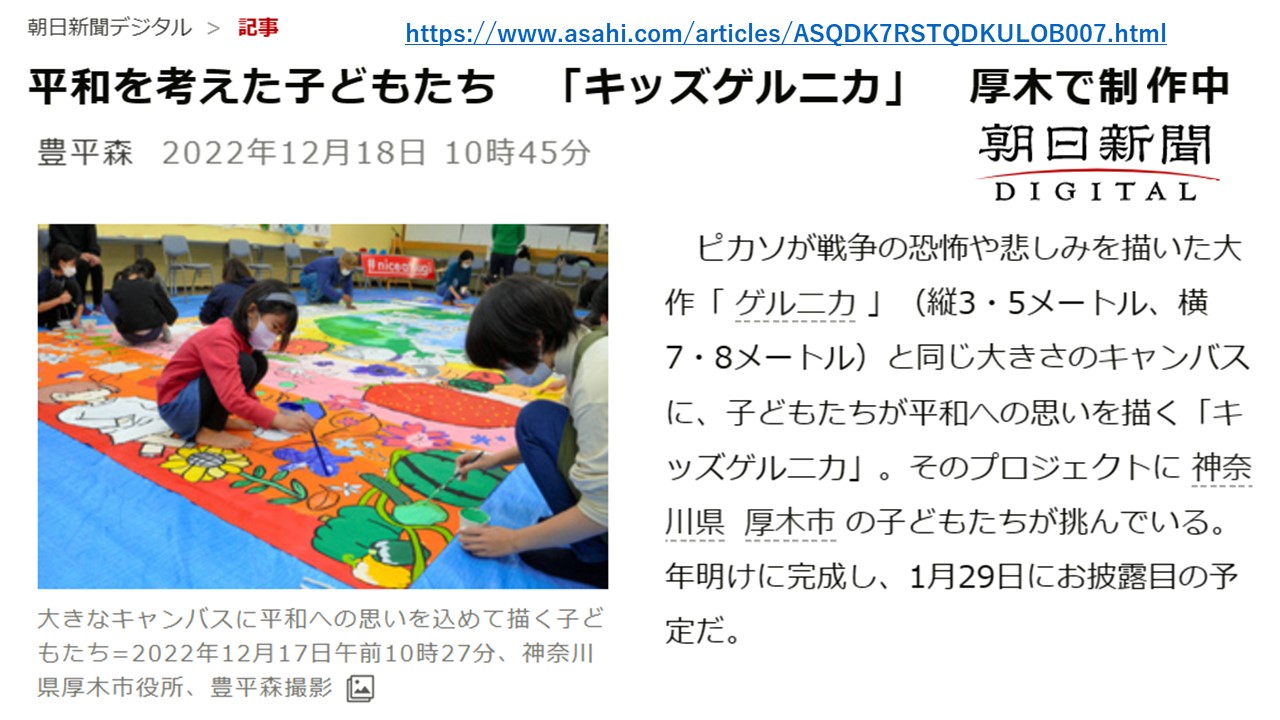

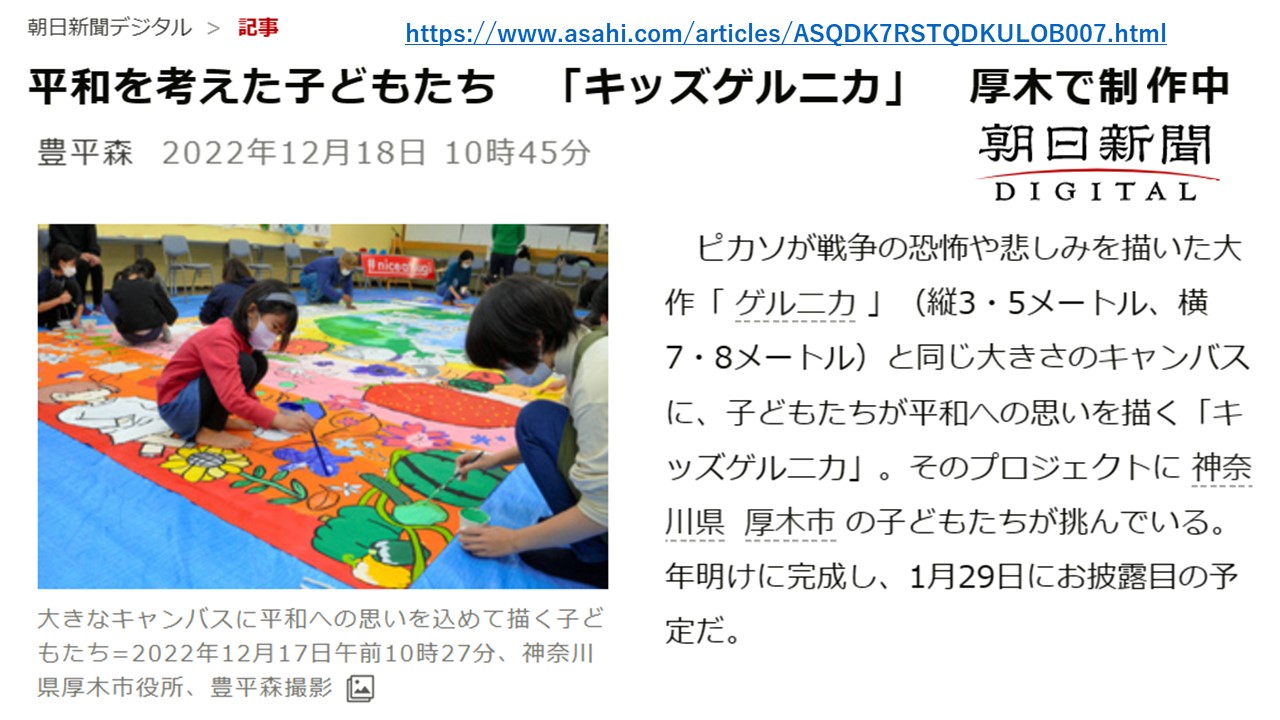

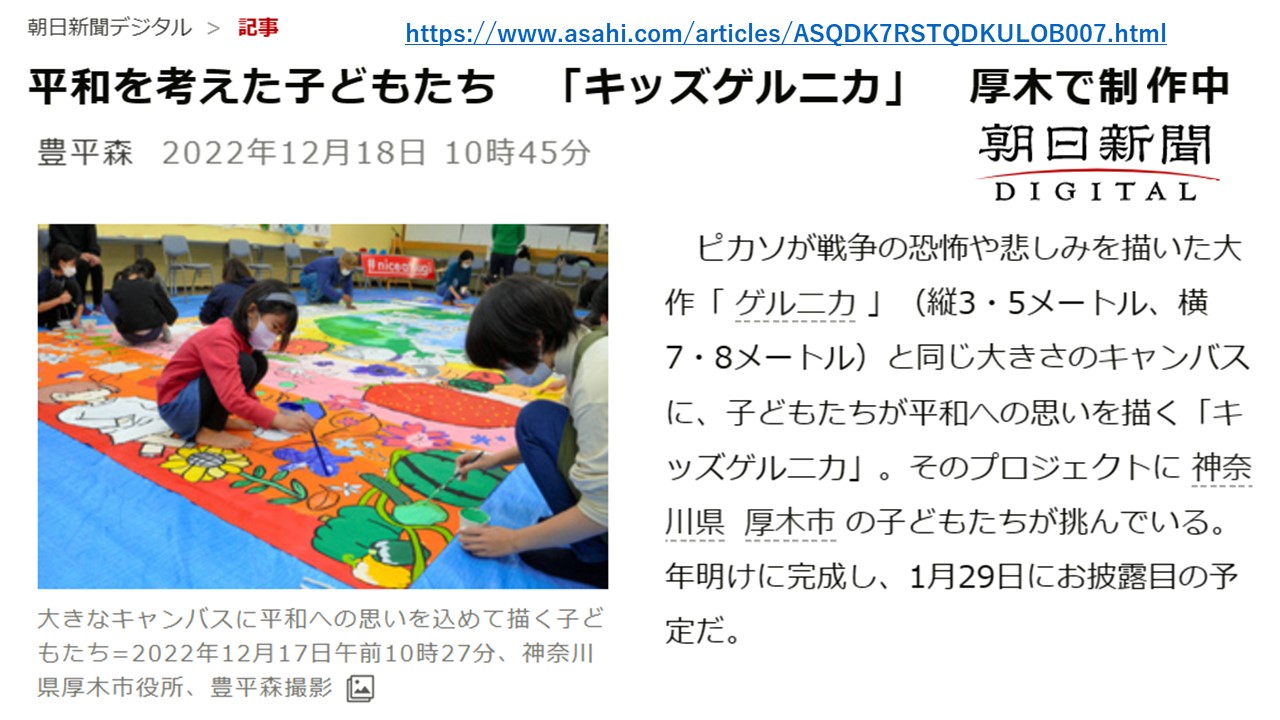

朝日新聞デジタル_2022_12_18_厚木市キッズゲルニカ.pdf

厚木キッズゲルニカ_2023_01_29.pdf

Atsugi-city_Kids_Gernica_Project_2023_1_29_creators.yahoo.co.jp(html)

++++++++++++++++++++++++++++++++++++++++++++++++++++++

https://www.asahi.com/articles/ASQDK7RSTQDKULOB007.html

朝日新聞デジタル_2022_12_18_厚木市キッズゲルニカ.pdf

++++++++++++++++++++++++++++++++++++++++++++++++++

++++++++++++++++++++++++++++++++++++++++++++++++++++++

厚木市荻野自然観察会のご紹介.html

++++++++++++++++++++++++++++++++++++++++++++++++++++++

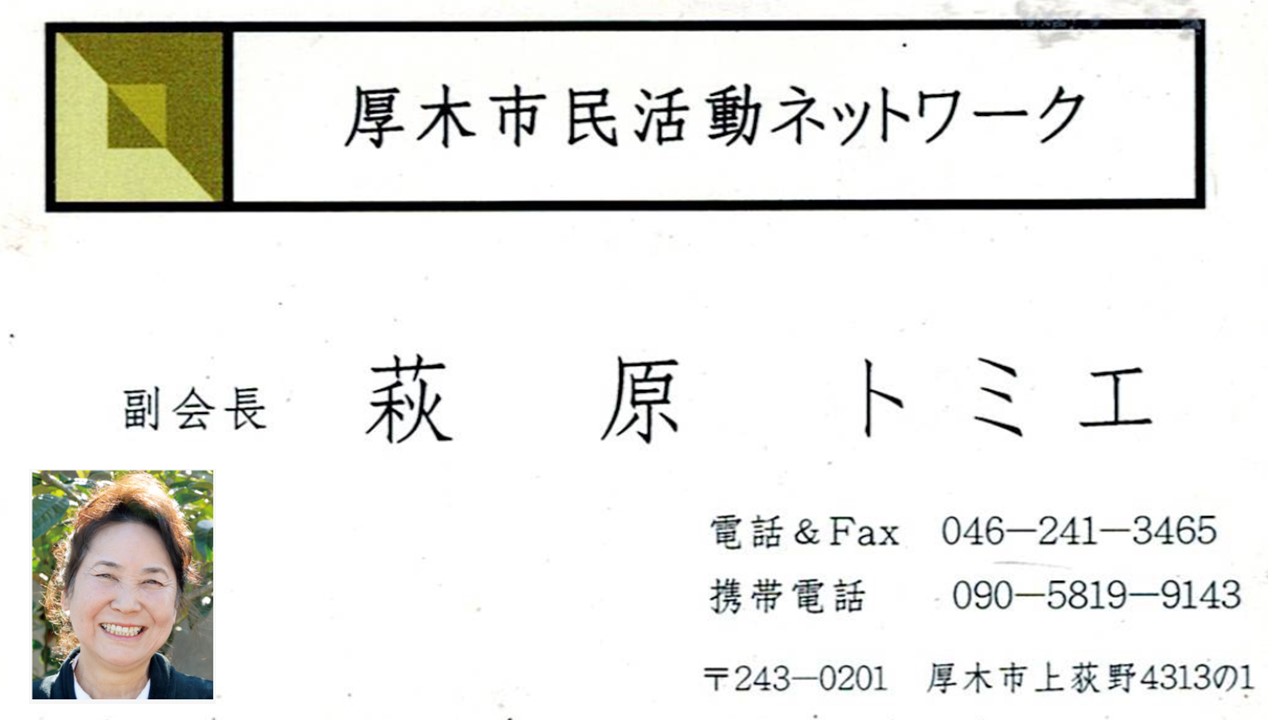

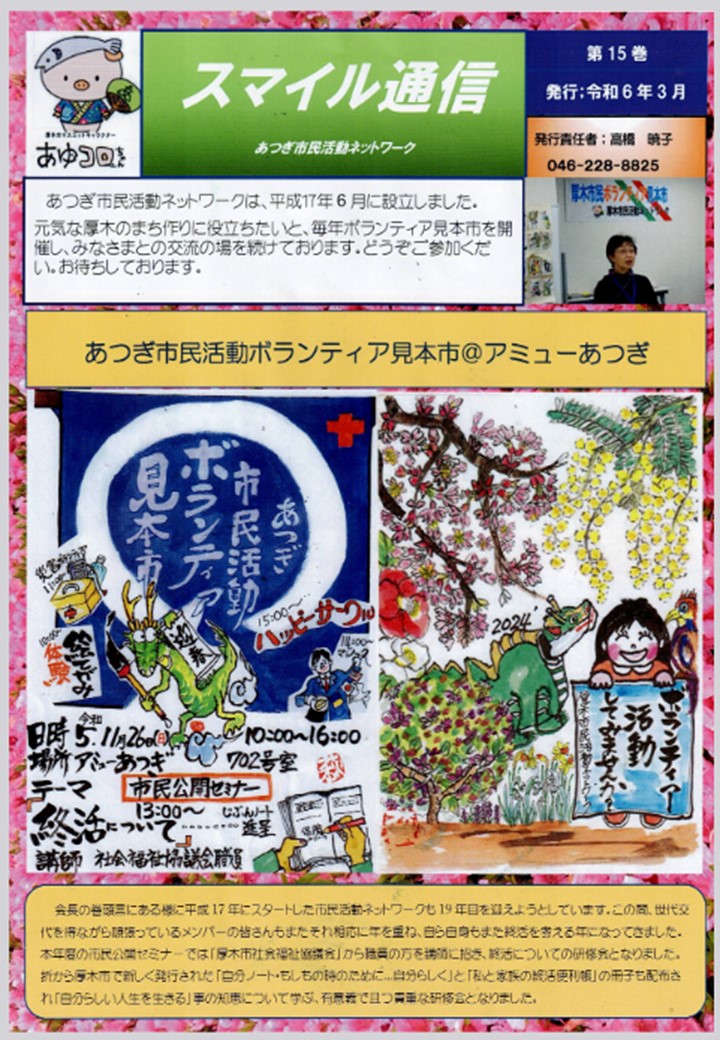

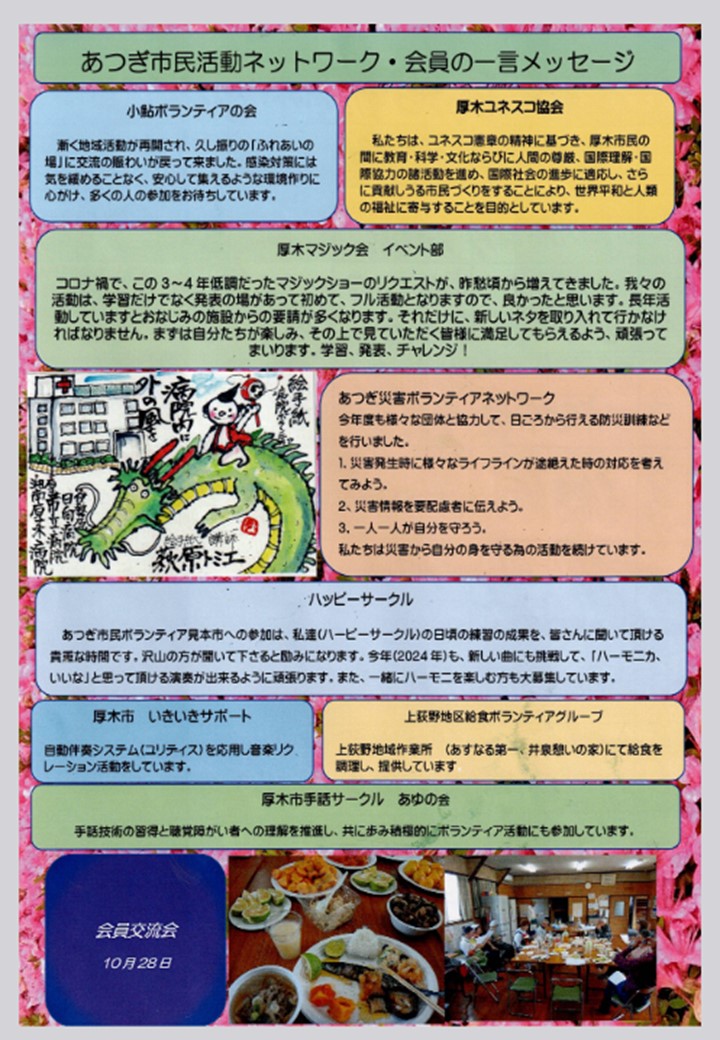

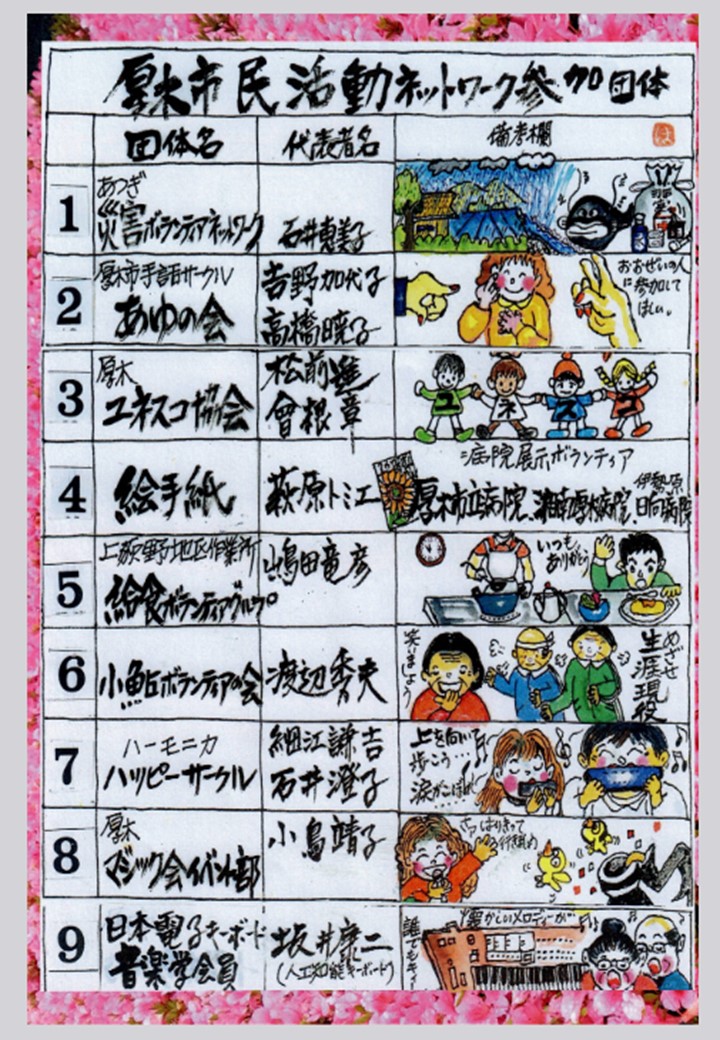

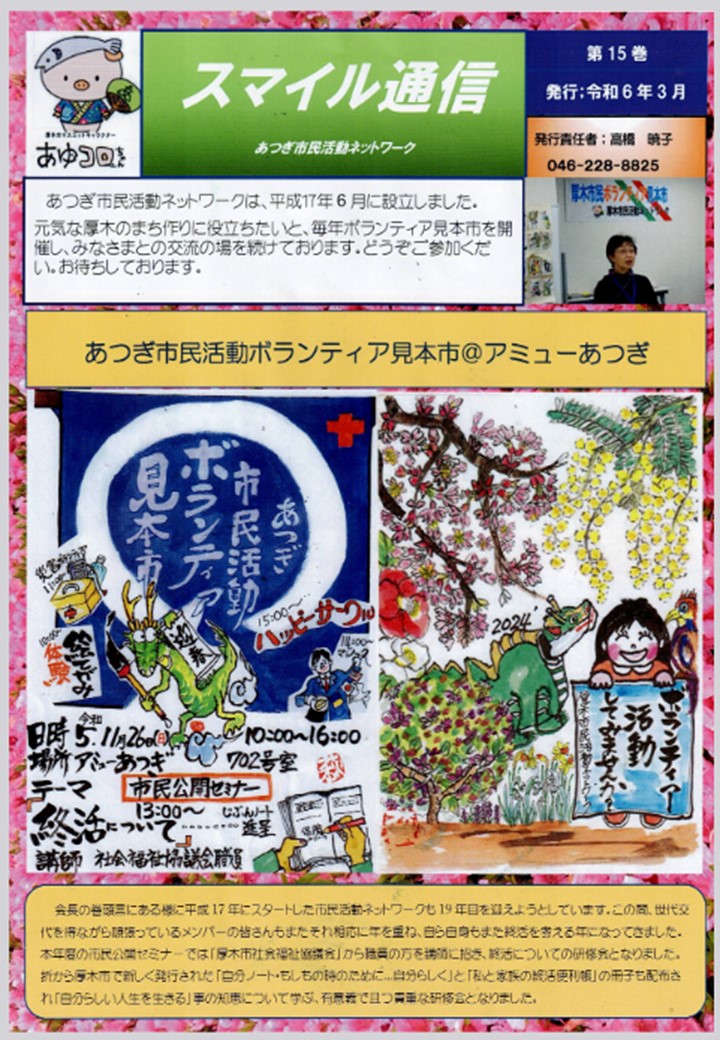

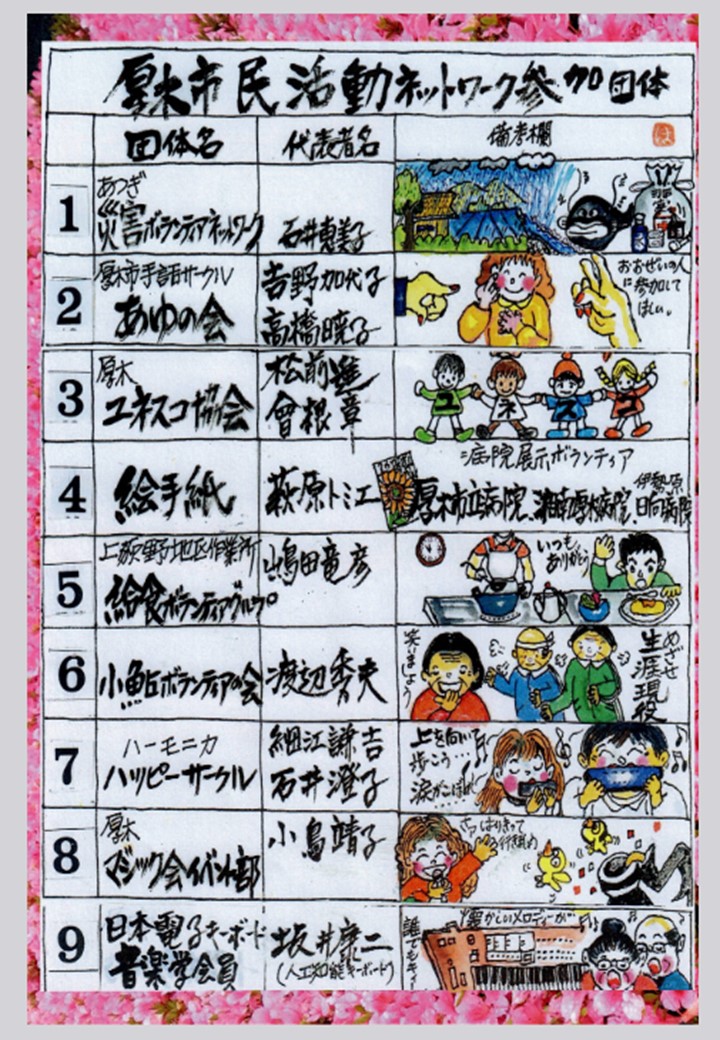

あつぎ市民活動ネットワーク_スマイル通信_2023年3月号第15巻_Page01

++++++++++++++++++++++++++++++++++++++++++++++++++++++

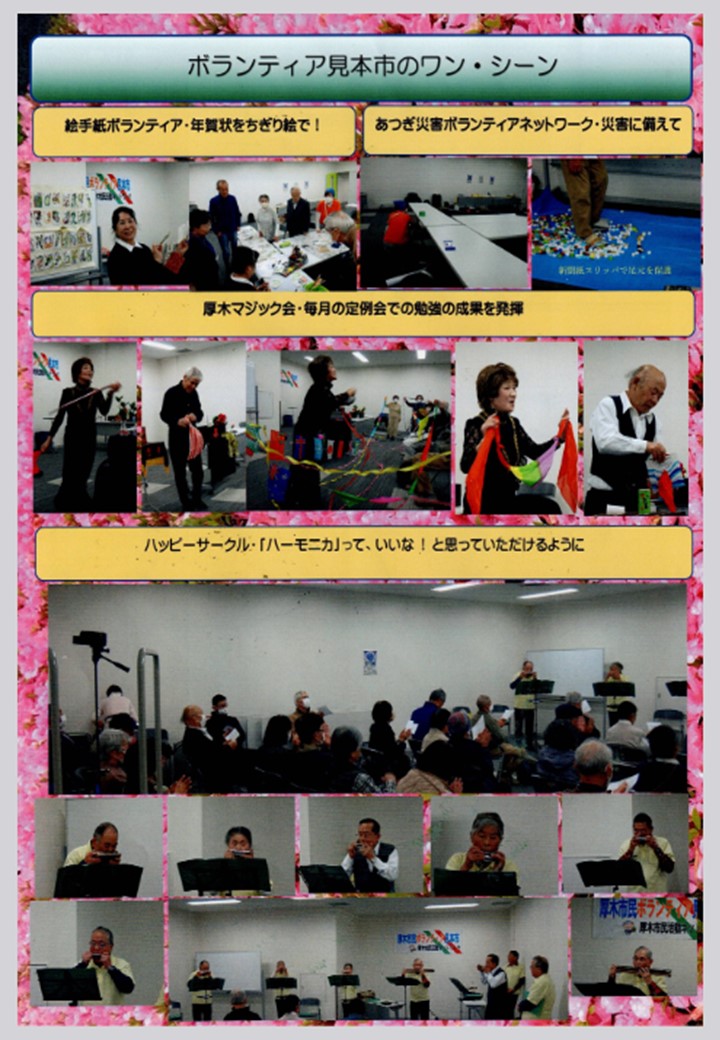

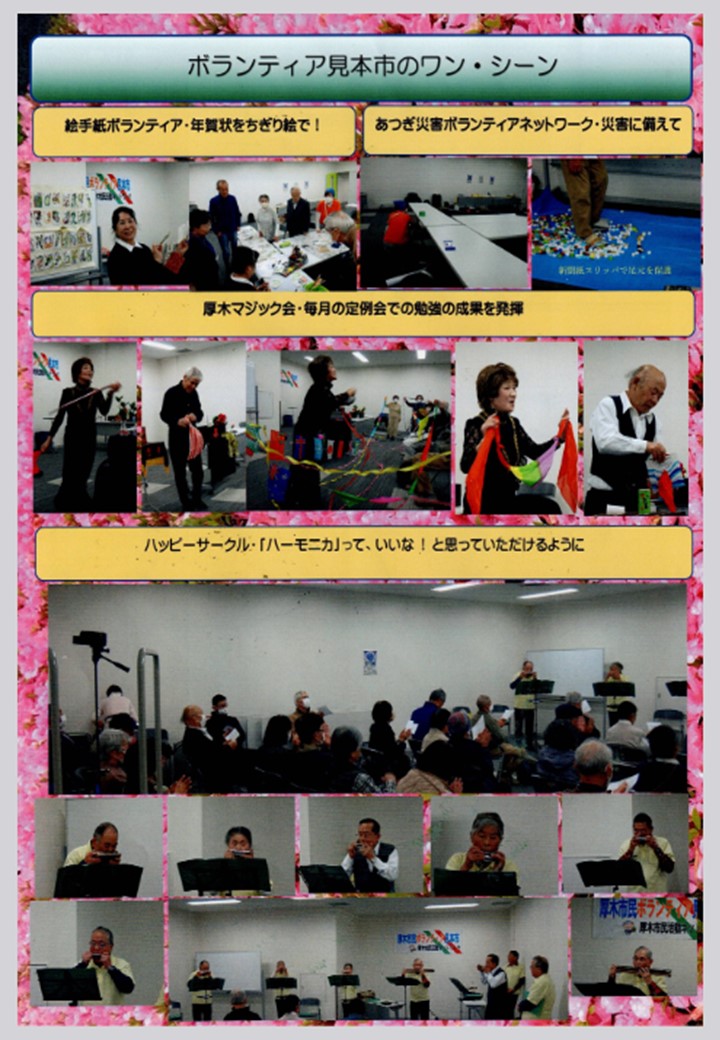

あつぎ市民活動ネットワーク_スマイル通信_2023年3月号第15巻_Page02

++++++++++++++++++++++++++++++++++++++++++++++++++++++

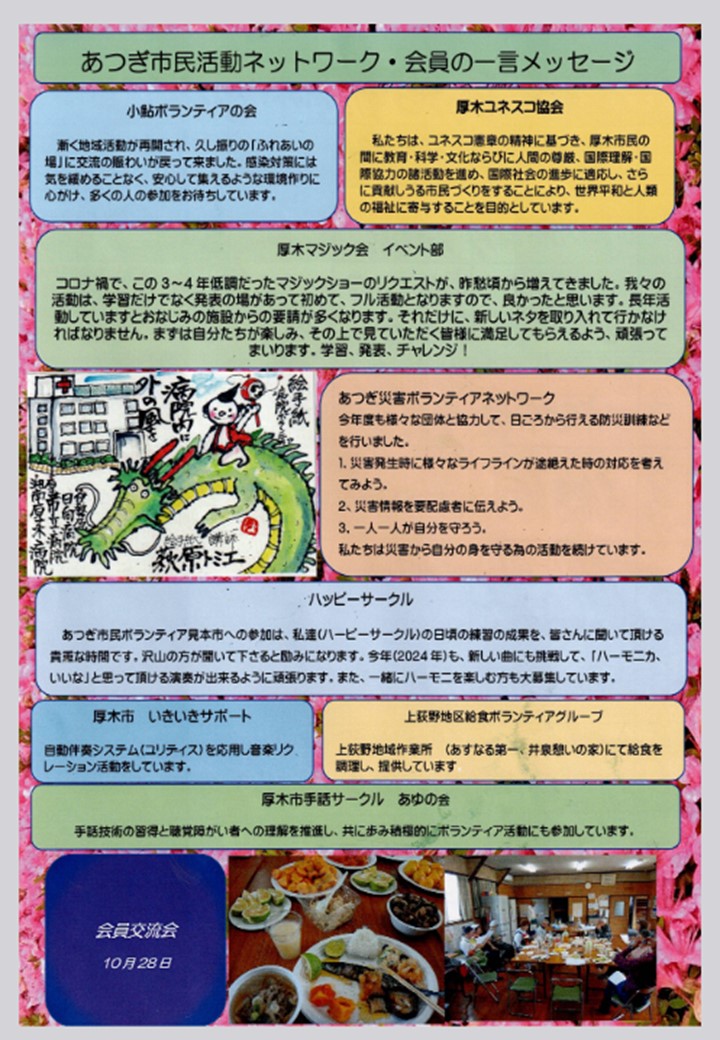

あつぎ市民活動ネットワーク_スマイル通信_2023年3月号第15巻_Page03

++++++++++++++++++++++++++++++++++++++++++++++++++++++

あつぎ市民活動ネットワーク_スマイル通信_2023年3月号第15巻_Page04

++++++++++++++++++++++++++++++++++++++++++++++++++++++

++++++++++++++++++++++++++++++++++++++++++++++++++++++

++++++++++++++++++++++++++++++++++++++++++++++++++++++

*********************************************************************

Hagiwara_Photo_Gallery.html

*********************************************************************

2022年8月12日

前回写真をUploadしてからも11ヶ月が過ぎました。

自宅の寝室の窓から見えるノウゼンカズラ(Campsis grandiflora)の花は

今が見ごろです。元気良く今年もつるを伸ばし今咲き誇っています。

20220812_001.JPG

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

++++++++++++++++++++++++++++++++++++++++++++++++++++++

神奈川県厚木市のコミュニティカフェ荻野.html

++++++++++++++++++++++++++++++++++++++++++++++++++++++

++++++++++++++++++++++++++++++++++++++++++++++++++++++

鳶尾カフェの常連客の鈴木歩(あゆむ)さんの「厚木田独歩」パソコン写仏のご紹介です

鳶尾カフェの常連客の鈴木歩(あゆむ)さんの徒歩旅の記録です

++++++++++++++++++++++++++++++++++++++++++++++++++++++

++++++++++++++++++++++++++++++++++++++++++++++++++++++

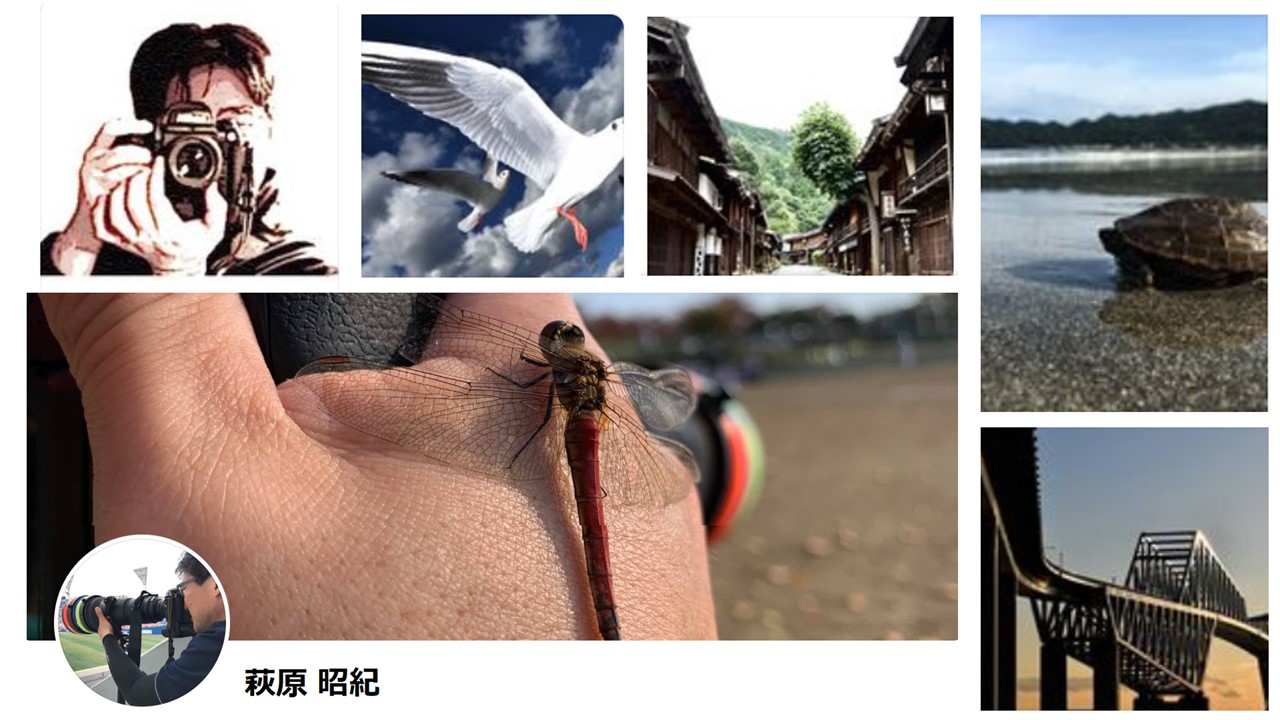

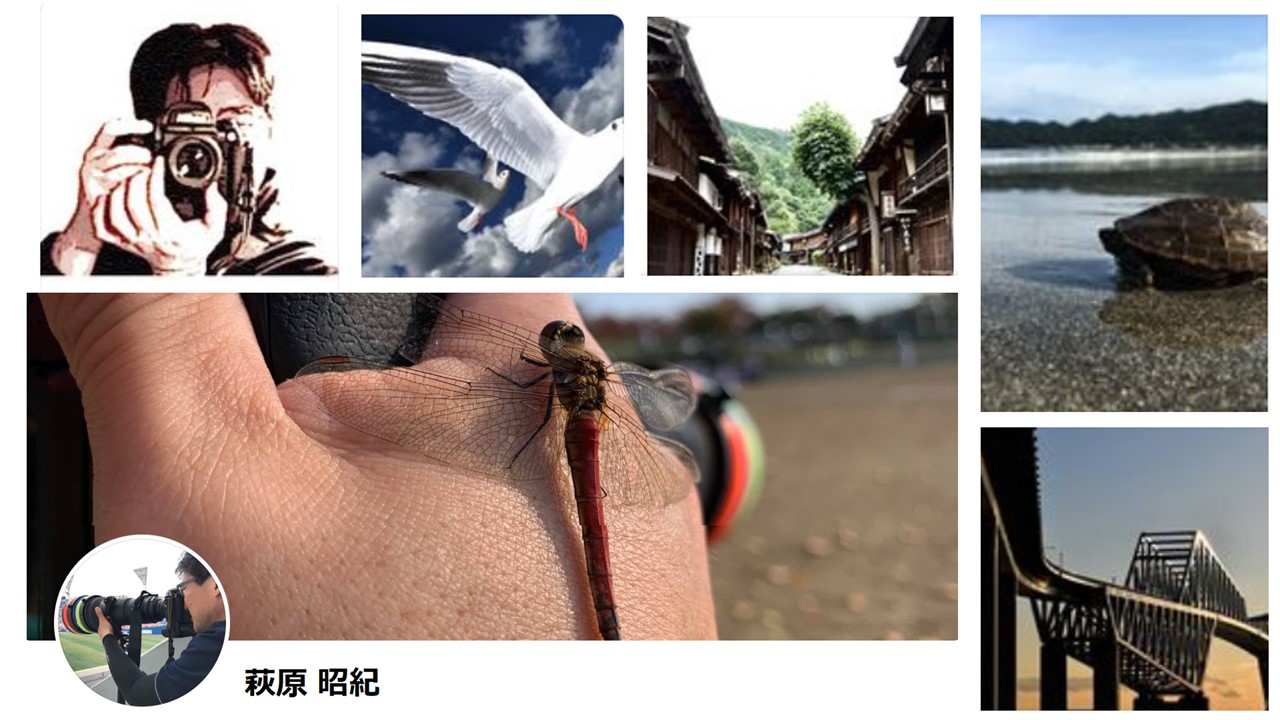

カメラマン萩原昭紀の活動紹介.html

++++++++++++++++++++++++++++++++++++++++++++++++++++++

Study Korean Language for Fun

++++++++++++++++++++++++++++++++++++++++++++++++++++++

Enjoy_Korean_Language_for_Fun/index.html

++++++++++++++++++++++++++++++++++++++++++++++++++++++

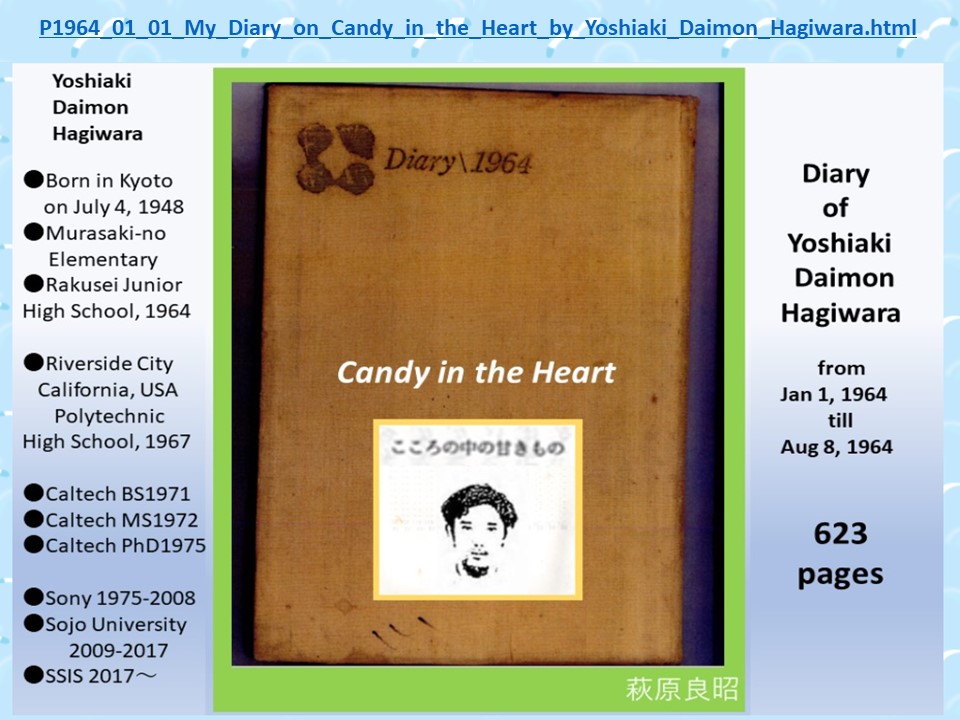

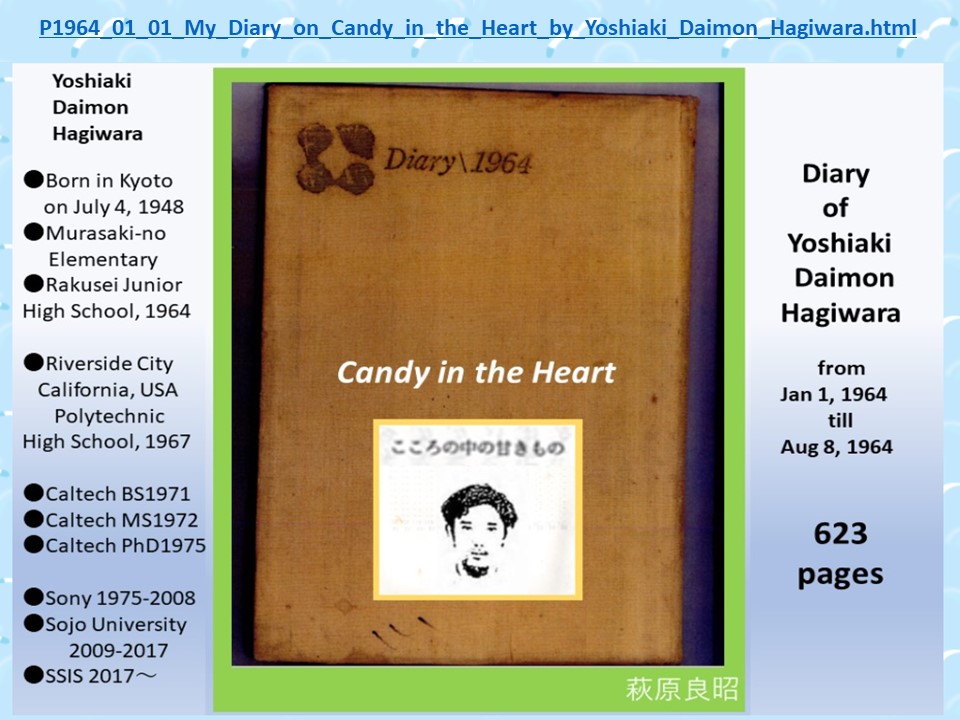

P1961_01_01_My_Diary_on_Candy_in_the_Heart/Candy_in_the_Heart.html

P1961_01_01_My_Diary_on_Candy_in_the_Heart/Candy_in_the_Heart.html

++++++++++++++++++++++++++++++++++++++++++++++++++++++

++++++++++++++++++++++++++++++++++++++++++++++++++++++

Publication_List_by_Yoshiaki_Hagiwara.html

Backups of Past AIPS Homepages.html

Sony_Image_Sensor_Story_by_Yoshiaki_Hagiwara.pdf

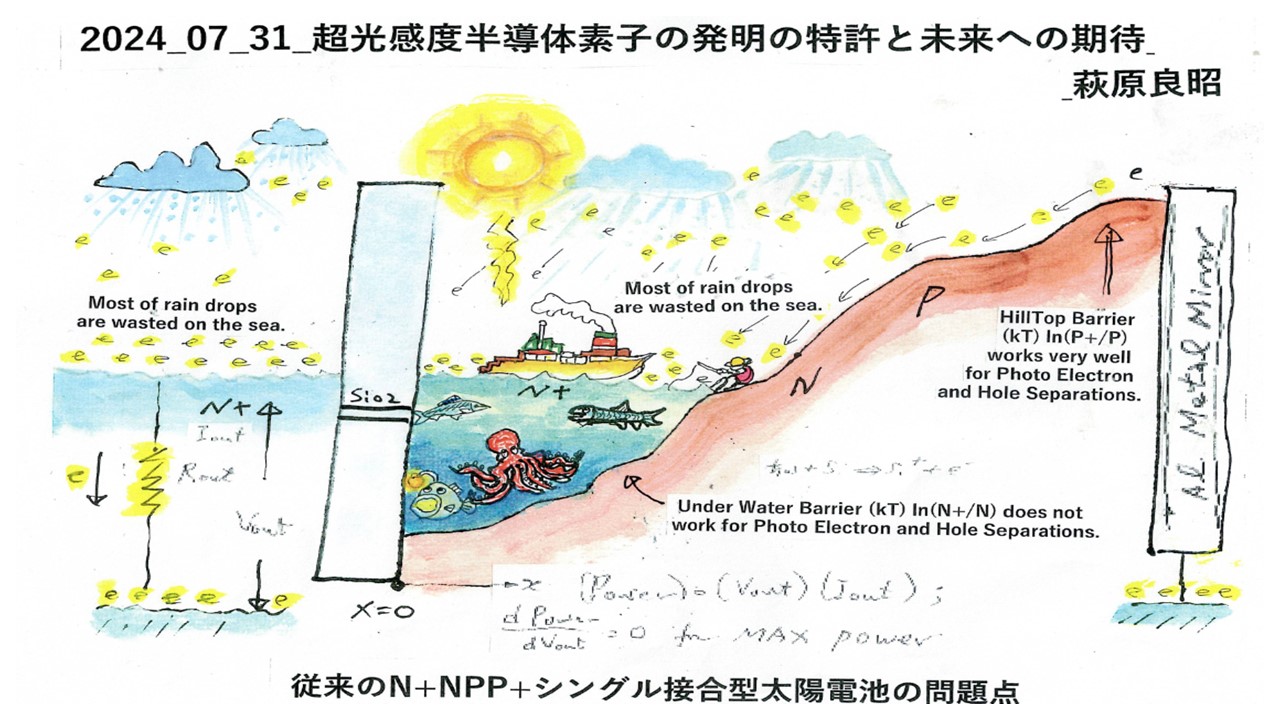

受光表面の電位は浮遊状態でflatであるSingle接合太陽電池の問題点.html

2024_05_日経エレクトニックス_ペロブスカイトのお株を奪うシリコン太陽電池.pdf

半導体未来館の設立のご提案です_萩原良昭.pdf

++++++++++++++++++++++++++++++++++++++++++

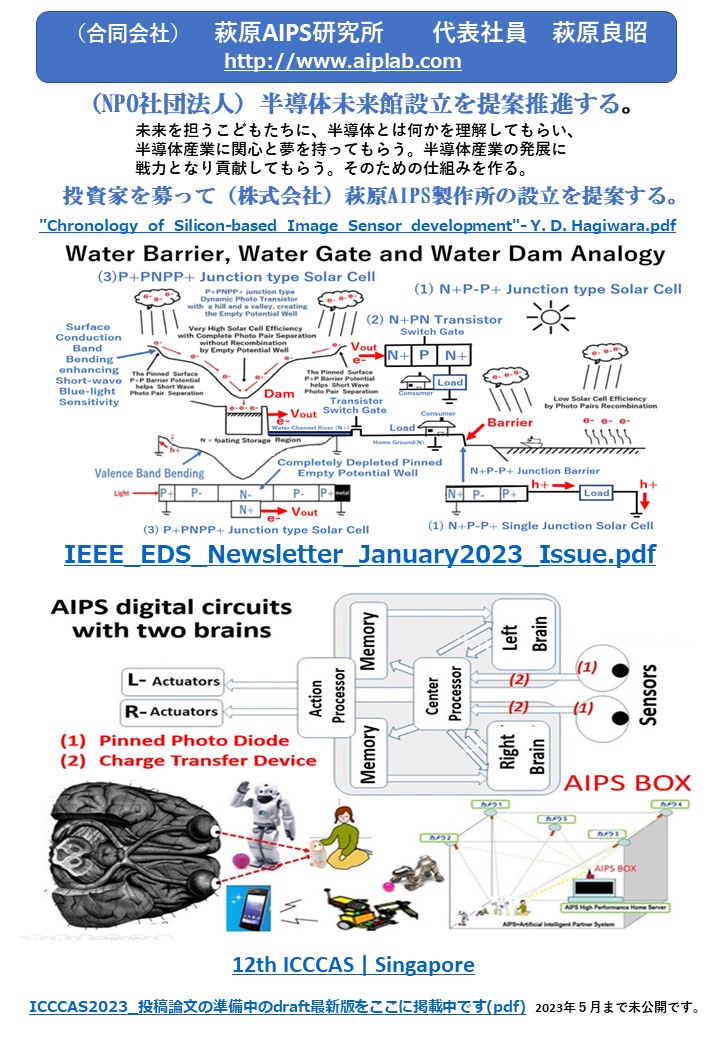

●COMPUTER や AI ROBOTの実現には、半導体は 重要な戦略的な存在である事は昔から理解されている。

萩原良昭の母校 Caltechの大先輩でもあり、米国Fairchild社とIntel社の創設者のGordon Moore が提唱した、

半導体の微細加工技術のScaling則に従い、1948年のトラジスターの誕生から半導体産業は発展した。

一般に半導体産業界では牧本WAVEと知られる、折からの半導体ブームの波に乗り、今は半導体の全盛期となった。

そのために、未来の半導体産業界の戦力と期待される若者の育成とその教育活動は重要となってきている。

++++++++++++++++++++++++++++++++++++++++++

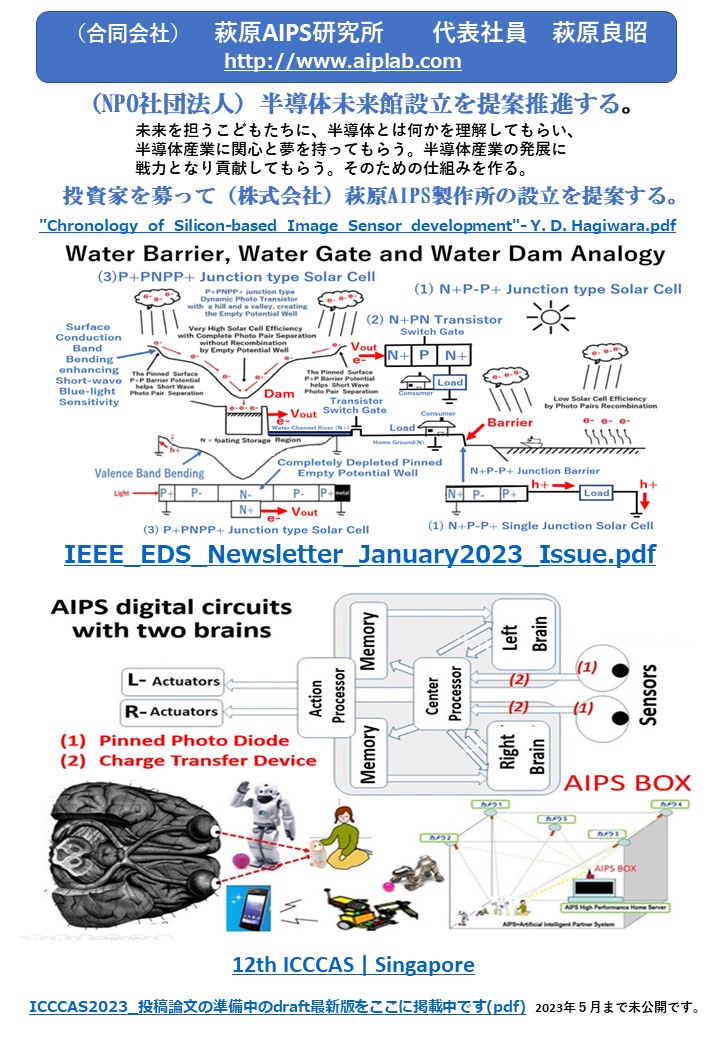

●長い歴史の中で、人類は水をコントロールすることにより、初めて農耕技術により人類の文明が発達した。

●まず、川のそばで田畑を耕し、川の水の氾濫を避けるため「堤防」を築いた。

半導体部品の1つである PNシングル接合のDIODE に対応する。DIODE は電流をBLOCKして「堤防」の様に機能する。

●次に、人類は、川から水を自在に田畑の取り込む為に、自由に開閉できる「水門」を築いた。

これは半導体部品の重要部品の1つである、米国ベル研が1948年に発明したTRANSISTOR に対応する。

このPNPダブル接合のTRANSISTOR は電流を自由自在にstopしたり流したりすることができる、「水門」の様に機能する。

●次の人類は、日照りで川の水は不足する干ばつ時のために、少ない水を大切に集め貯める、貯水池(ダム)を築いた。

これは半導体部品の重要部品の1つとなった、もとSony(萩原良昭)の1975年発明のHADセンサー素子に対応する。

++++++++++++++++++++++++++++++++++++++++++

このSONY(萩原)が1975年に発明し1978年開発しSSDM1978の学会で発表した超光感度半導体受光素子は、

その後、英語圏のIEDM1984の国際学会でも注目され、1984年には、KODAK社がPinned Photodiodeと名付けた。、

1980年に開発品を新聞発表した後は、ソニーは生産技術とビジネス化のために沈黙を続けた。

萩原良昭も商品化を優先し、九州でのソニー半導体工場の立ち上げに注力した。

その生産部隊と開発部隊が一体となり、SONYのTOPの方針に従い、1987年に商品化に成功した。、

ソニー商標「ソニーHADセンサー素子」としてと登録し、ビジネス化に大成功した。

日本の半導体産業が衰退する中、ソニーの超光半導体素子は、一人勝ちを果たし、世界の市場を制覇し現在に至る。

その後、超光感度のCCDビデオカメラが一時は注目されたが、今はCCDビデオカメラは市場から消えた。

しかし今でも萩原良昭が26歳に時に発明し、地味な静かな開発努力を続けた、

大切な光エネルギー(光子)を電気エネルギー(光電子)に効率良く変換する、

超光感度の受光素子は、CCDビデオカメラにもCMOSビデオカメラに使用された。

今の世界中のビデオカメラやスマフォや、天文学の宇宙の望遠鏡にも、「縁の下の力持ち」となり活躍している。

●SONYは1975年萩原良昭発明の超光感度受光素子のHADセンサー素子をビデオカメラやスマフォに採用した。

世界中のすべての企業が、萩原が26歳に発明した超光感度の電子の目を人類の財産として今では使用している。

++++++++++++++++++++++++++++++++++++++++++

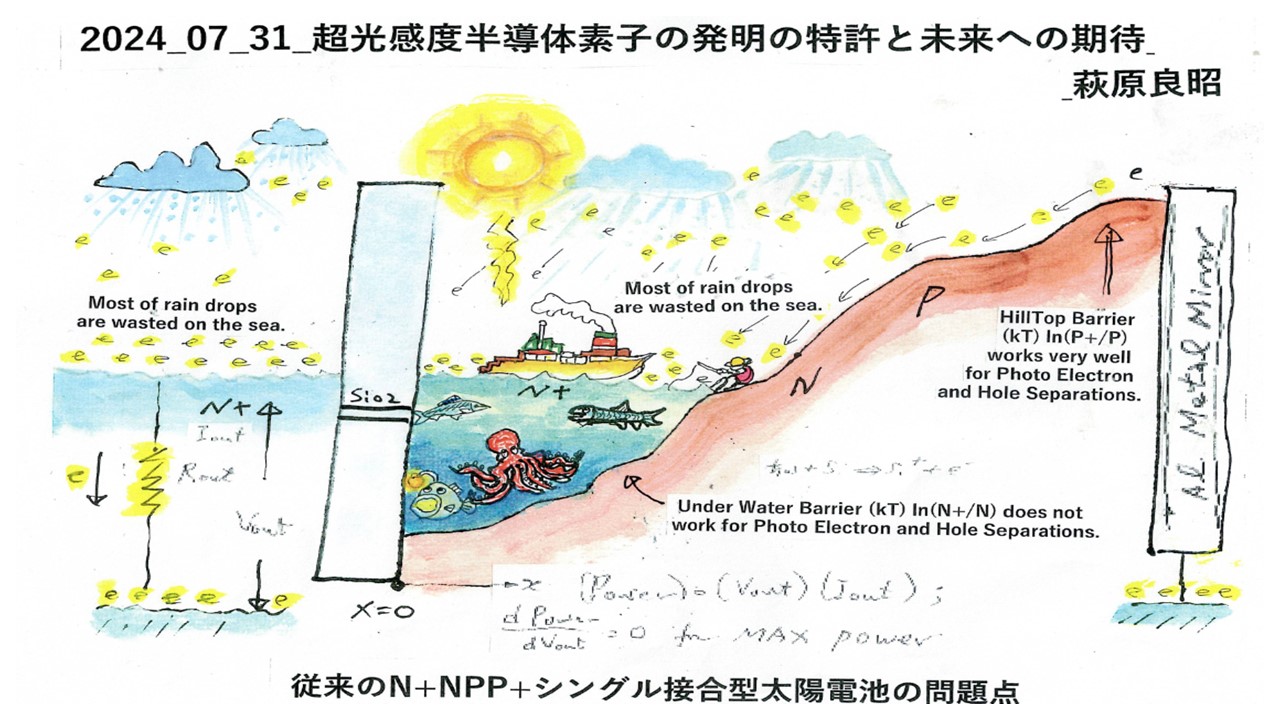

●それから50年が過ぎた。76歳になった萩原良昭は、今も半導体産業の発展を夢する少年である、

自分が1975年に発明した超光感度の電子の目を、今度は、

光エネルギーを電気エネルギーに効率良く変換する、

超光感度の、新型のDynamic Photo Transisor 型太陽電池を実現を夢見ている。

●エネルギーと食料問題は、日本でけでなく、世界の永遠の問題である。

持続可能な、自然にやさしい、地球にやさしい SDGs実現の為に、

萩原良昭の夢は、彼一人だけの夢でなく、

日本の世界の人々の夢として、今も大きく膨らむ。

従来のN+NPP+シングル接合型のSolar_Cellの問題点.pdf

Pinned_Photodiode_type_Solar_Cell_See_JPA1975_131313_and_JP6828108.html

超光感度半導体素子の発明の特許と未来への期待_萩原良昭.html

日本の産業のコメとして戦略的に重要な半導体電子部品の基本知識.html

P+PNPP+ダブル接合_Pinned_Photodiode型太陽電池の提案_萩原良昭.html

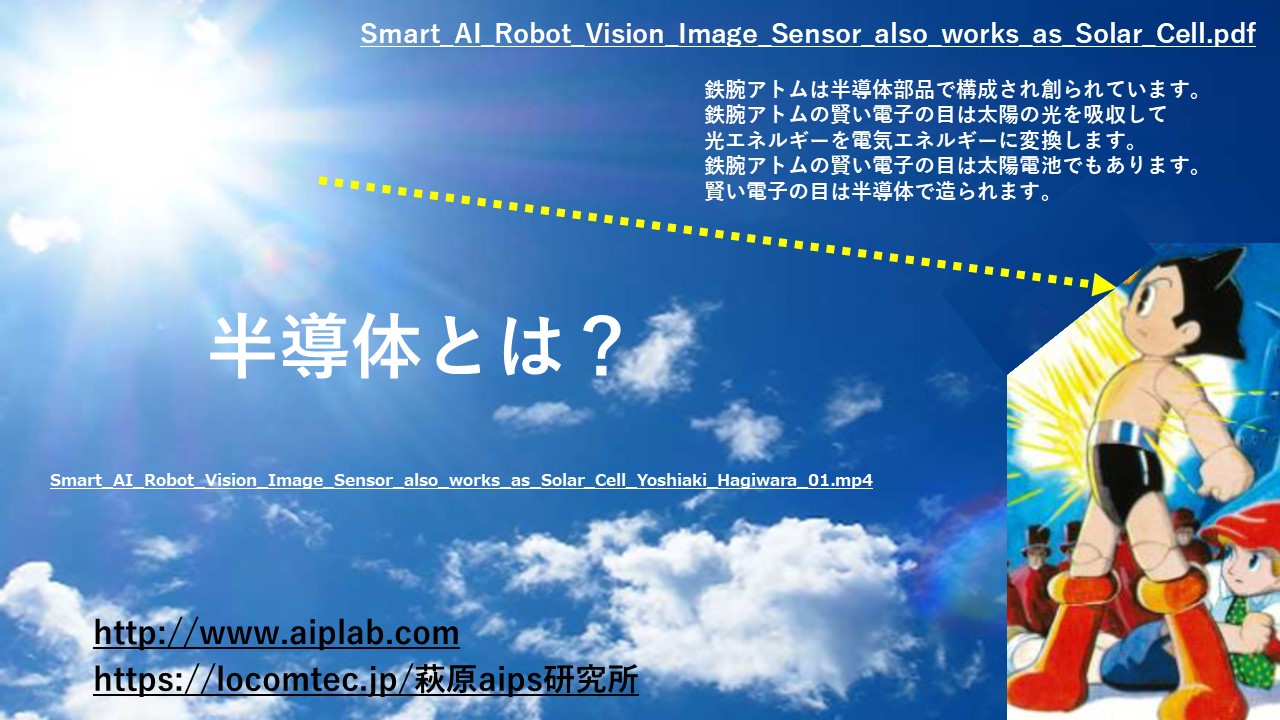

半導体とは?萩原良昭.html

萩原良昭講師の半導体教育講座.html

+++++++++++++++++++++++++++++++++++++++++++++

人間にやさしい、太陽光発電をエネルギー源とする、

SDDs理念にかなった萩原AIPSロボットの開発資金の一般応募です。

AIPS=Artificial Intelligent Partner System

+++++++++++++++++++++++++++++++++++++++++++++

地球にやさしい、SDGsの目的にかなった、人工知搭載ロボットの開発

試作の資金を一般募集します。この萩原AIPSロボットはマンガで

おなじみの鉄腕アトムとは違い、原子力発電の汚染問題はありません。

エネルギー源として、原子力発電は萩原AIPSロボットには使いません。

太陽光発電をエネルギー源とし、萩原AIPSロボットの電子の目は、

太陽を見つめるだけで、太陽光から電気エネルギーを得る事ができます。

+++++++++++++++++++++++++++++++++++++++++++++

+++++++++++++++++++++++++++++++++++++++++++++

HOP(萩原応援プロジェクト)個人活動応援金が 現在206万円になりました。ありがとうございます!

HOP_応援募金活動報告_応援ありがとうございます_萩原良昭.html

+++++++++++++++++++++++++++++++++++++++++++++

一般応援募金講座:

三菱UFJ銀行 厚木支店 店番707

普通口座 0456308

名義人 萩原良昭(ハギワラ ヨシアキ)

下記 MAIL ADDRESS への応援メッセージをお願いします。

hagiwara-yoshiaki@aiplab.com

+++++++++++++++++++++++++++++++++++++++++++++

************************************************************************************

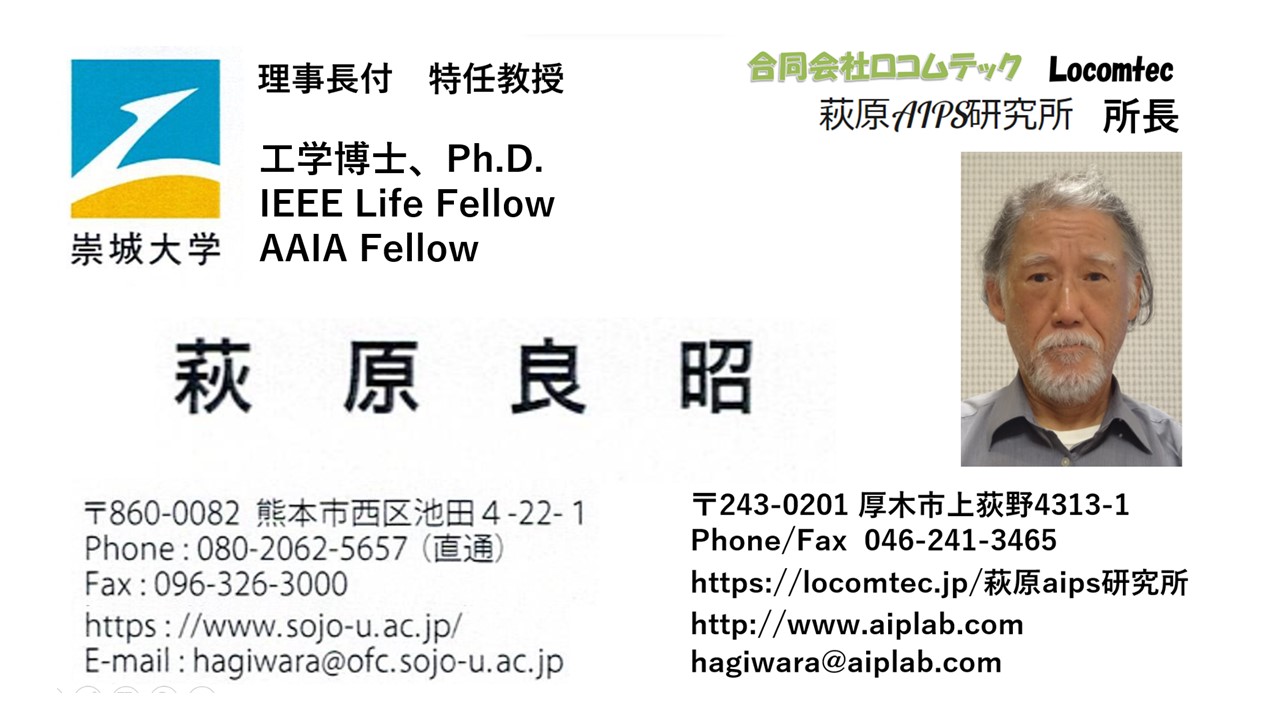

Locomtec.jp/萩原aips研究所のご案内

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Publication_List_by_Yoshiaki_Hagiwara.html

設立の提案_LOCOMTEC社萩原aips研究所.jpg)

半導体未来館(マンガ館)設立の提案_LOCOMTEC社萩原aips研究所.pdf

Smart_AI_Robot_Vision_Image_Sensor_also_works_as_Solar_Cell_Yoshiaki_Hagiwara.pdf

++++++++++++++++++++++++++++++++++++

半導体未来館(マンガ館)の参考教材

Smart_AI_Robot_Vision_Image_Sensor_also_works_as_Solar_Cell_Yoshiaki_Hagiwara.pdf

Smart_AI_Robot_Vision_Image_Sensor_also_works_as_Solar_Cell_Yoshiaki_Hagiwara_01.mp4

++++++++++++++++++++++++++++++++++++++++++++++++++++++

Locomtec.jp/萩原aips研究所のご案内

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Hagiwara_履歴_2023_03_24.pdf

++++++++++++++++++++++++++++++++++++++++++++++++++++++

Publication_List_by_Yoshiaki_Hagiwara.html

Hagiwara_履歴_2023_03_24.pdf

++++++++++++++++++++++++++++++++++++++++++++++++++++++

++++++++++++++++++++++++++++++++++++++++++++++++++++++

Back-ups AIPS Home Pages

++++++++++++++++++++++++++++++++++++++++++++++++++++++

AIPS_240822.html

AIPS_240309.html

AIPS_230316.html

AIPS_221231.html

AIPS_220823.html

AIPS_220131.html

AIPS_211226.html

AIPS_211206.html

AIPS_211107.html

AIPS_210929.html

AIPS_210906.html

AIPS_210811.html

AIPS_210404.html

AIPS_210301.html

AIPS_210217.html

AIPS_210215.html

AIPS_201209.html

AIPS_200627.html

AIPS_190925.html

AIPS_190712.html

AIPS_181129.html

AIPS_090628.html

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

https://www.sojo-u.ac.jp hagiwara(@)ofc.sojo-u.ac.jp

https://www.ssis.or.jp hagiwara(@)ssis.or.jp

http://www.aiplab.com hagiwara(@)aiplab.com

https://locomtec.jp/萩原aips研究所

https://ja.wikipedia.org/wiki/萩原良昭

https://en.wikipedia.org/wiki/Yoshiaki_Hagiwara

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

Return to Top Home Page of Yoshiaki Hagiwara (AIPS)

http://www.aiplab.com

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++

搭載のロボット.jpg)

設立の提案_LOCOMTEC社萩原aips研究所.jpg)